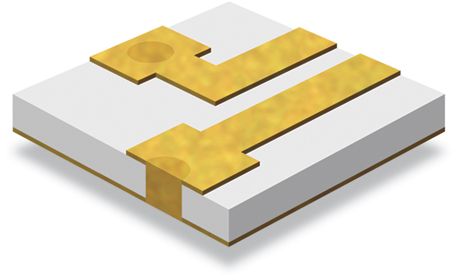

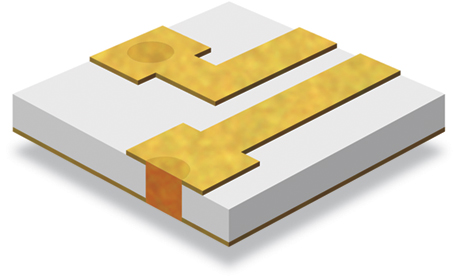

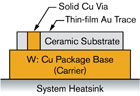

Vias: Au or Cu Solid Filled

| Company | Technologies | Capabilities | Design Guidelines | Products | Other |

Introduction |

Polyimide Bridges |

Photomasks |

Standard Dimensions, Tolerances |

Inductor Coils |

Home |

Quality Assurance |

Solder Dams |

Substrates |

CAD Data Guidelines |

Inductor Coils Eng. Kit |

Contact Us |

Directions |

Laser Diode Submounts |

Material Specifications |

Material and Conversion Tables |

Microstrip Transmission Lines |

Careers |

Careers |

Vias: Plated Through |

Ion Beam |

Thermal Performance |

Transmission Lines Eng. Kits |

Terms of Use |

Sales Rep’s |

Vias: Au or Cu Solid Filled |

Aluminum Bonding Pads |

Aging Equation |

Stand Off/Isolation Pads |

Privacy Policy |

Contact Us |

Edge Wraps |

Laser Machining/Drilling |

Safe Current Limits |

ATP Bond Qualification Coupons |

|

Gold Bumping |

Backside Burnishing |

Design Resources |

Product Samples |

YouTube |

|

Fractal Fasten |

Standard Metallizations |

Packaging/Chip Trays |

|||

Integrated TaN Resistors |

Thin Film Resistor and Multi-Tap |

||||

Laser Resistor Trimming |

|||||

Serialization |